SIT 212, TP4⚓

Mme Charlotte LANGLAIS - Dépt. Mathematical and Electrical Engineering

Simulation de signaux et briques de transmission - TP4 : Synthèse et implantation matérielle d’une chaîne de transmission numérique sur circuit reconfigurable

Introduction⚓

Cette séance de Travaux Pratiques est une initiation à la conception de circuits intégrés numériques. Elle permet de découvrir les différentes étapes de la description d’une architecture en VHDL (langage dédié à l’électronique) jusqu’au test sur circuit reconfigurable FPGA (Field-Programmable Gate Array), le tout avec un outil professionnel, Vivado du fondeur de circuits Xilinx. Le second objectif de ce TP est d’illustrer certaines notions de communications numériques, telles que le choix d’un mapping efficace, ou l’influence du bruit sur la transmission, tout en concevant un émetteur et un récepteur à partir d’une description matérielle. Cette séance de TP est donc complémentaire des séances de SIT213 dédiées à l’implémentation d’une chaîne de transmission en logiciel avec un processeur généraliste.

Les grandes étapes de la conception d’un circuit sur FPGA sont les suivantes :

- conception de l’architecture du circuit sous forme de blocs/modules organisés hiérarchiquement,

- description des modules qui peut se faire par l’intermédiaire de langages de description matérielle (VHDL ou Verilog entre autres) ou d’outils de CAO proposant des modules déjà conçus paramétrables,

- simulation fonctionnelle de chaque module,

- intégration des modules pour réaliser le circuit complet,

- simulation du circuit complet,

- synthèse du circuit transformant la description hiérarchique en liste de composants logiques (portes élémentaires connectées),

- simulation post-synthèse pour vérifier que le modèle synthétisé est conforme au modèle initial,

- implantation physique qui consiste à traduire la liste précédente en liste de composants de la technologie cible (un FPGA donné par exemple), puis à les placer sur la cible matérielle et à les router,

- simulation post-placement-routage pour vérifier la conformité des performances,

- configuration(programmation) du circuit puis test du circuit sur carte.

Chacune des étapes de simulation et de test peut déclencher un retour en arrière plus ou moins important en cas d’échec.

En pratique, vous suivrez un flot simplifié, en bénéficiant du travail préparatoire des enseignants :

Phase 1 Description et simulation de modules combinatoires simples⚓

- une description « à trous » en VHDL est fournie et doit être complétée sur la base de la description qui en est donnée ;

- chaque module VHDL est ensuite simulé et corrigé si nécessaire.

Phase 2 Simulation du circuit complet⚓

Le circuit complet est simulé et le résultat analysé. Les résultats de simulation sont comparés aux résultats théoriques.

Phase 3 Synthèse, placement, routage et test du circuit complet⚓

- le flot de « compilation » matérielle doit être paramétré puis lancé ;

- le résultat de ce flot est analysé puis testé sur carte.

Présentation de la chaîne de transmission⚓

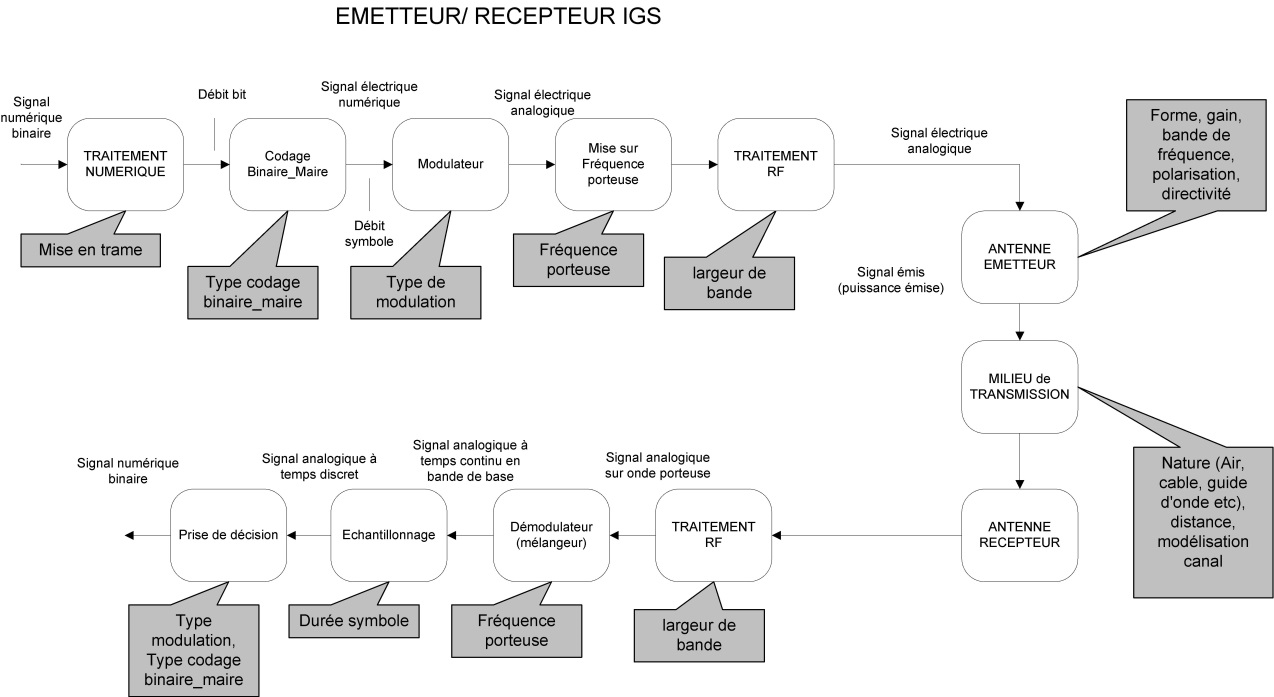

Afin d’illustrer le flot de conception de circuit numérique, nous choisissons de concevoir un émetteur et un récepteur d’une chaîne de transmission numérique en bande de base. La chaîne de transmission générique est représentée sur la figure ci-dessous. Elle contient l’ensemble des traitements numériques et analogiques nécessaires à la transmission de l’information sur un milieu de transmission.

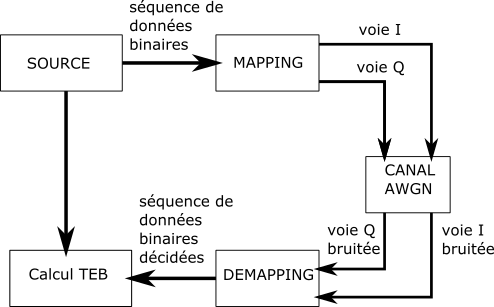

Dans ce TP, nous souhaitons émuler une transmission numérique en bande de base sur un circuit numérique reconfigurable de type FPGA. Le schéma simplifié de la transmission, telle qu’elle sera émulée sur le circuit FPGA, est donné figure ci-dessous. Contrairement à une transmission réaliste, toutes les fonctions émission, canal et réception sont placées sur la même carte. Dans la « vraie vie », l’émetteur et le récepteur ne sont pas co-localisés. Ce type de prototype matériel permet, par exemple, de vérifier les performances d’une modulation pour des taux d’erreurs binaires extrêmement bas du fait de la rapidité des opérations réalisées par le FPGA.

La source génère une séquence pseudo-aléaoire de bits en série. Le bloc mapping convertit la séquence binaire en deux signaux qui représentent la voie I et la voie Q du symbole complexe de modulation de type MAQ16 (Modulation d'Amplitude en Quadrature à 16 états). Le canal à bruit blanc additif gaussien (\emph{Additive White Gaussian Noise}, AWGN) permet de modéliser une source de bruit thermique ainsi que la perte en espace libre. Il est paramétré à partir du rapport signal-sur-bruit (\emph{signal to noise ratio}, SNR). Dans notre contexte, comme la puissance du signal en entrée du canal ne varie pas, c'est la variance du bruit généré par le canal \(\sigma_b^2\) qui est modifiée, telle que \(SNR = 10 \textrm{log}_{10} \frac{1}{2 \sigma_b^2}\). En sortie, les deux voies I et Q sont donc bruitées. Le demapping a pour rôle d'appliquer la règle du maximum de vraisemblance afin de décider des bits qui ont été émis. En sortie, on obtient une séquence de données binaires décidées, qui va pouvoir être comparée à la séquence qui a été émise grâce au bloc de calcul du taux d'erreurs binaires (TEB).

Présentation du circuit à concevoir : MAQ16⚓

Fonctions principales⚓

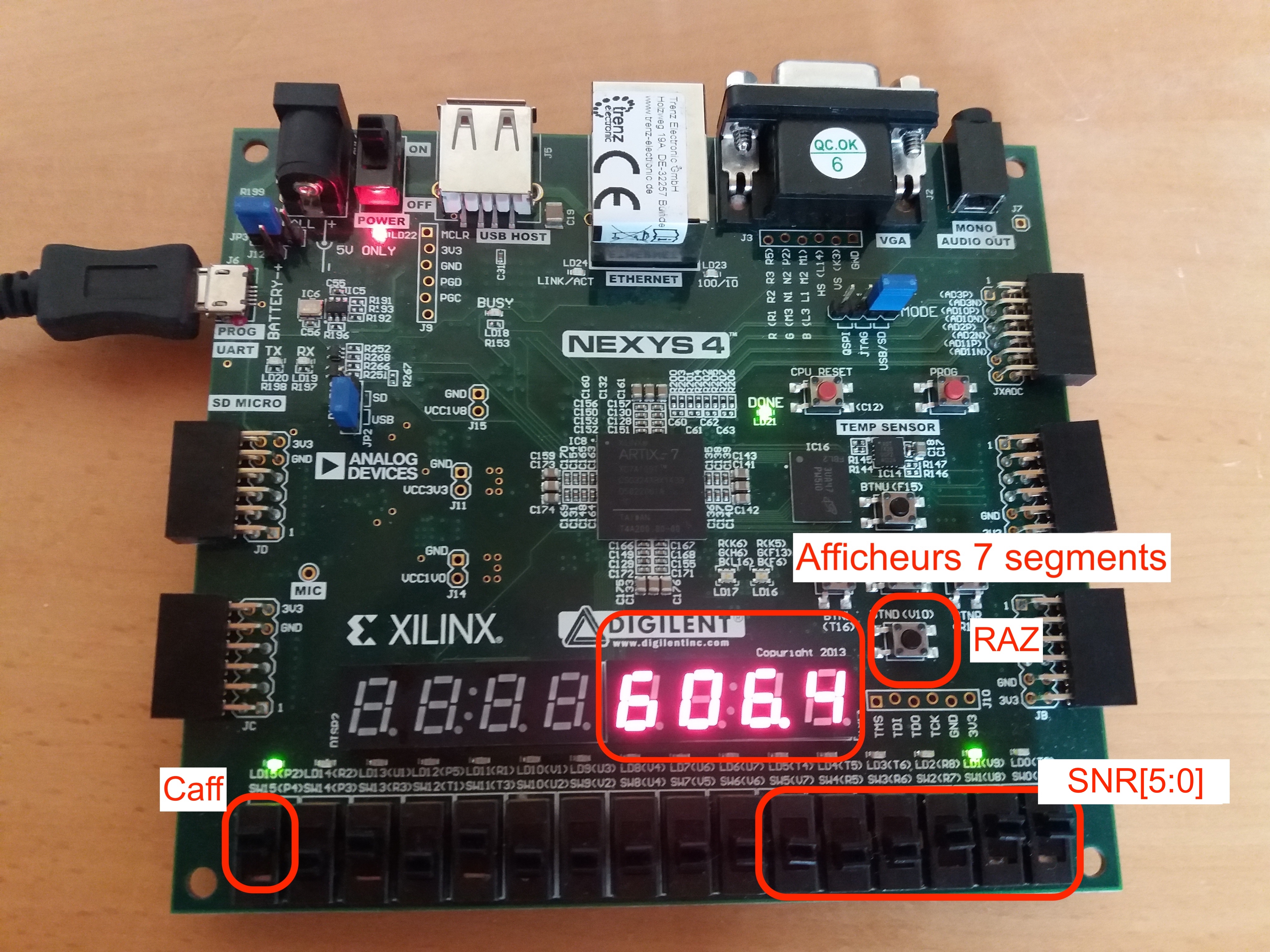

Le circuit à concevoir permet d'émuler une chaîne de transmission simplifiée en bande de base qui comprend un émetteur intégrant une modulation MAQ16, un canal à bruit blanc additif gaussien et un récepteur qui réalise la détection binaire puis calcule le taux d'erreurs binaires correspondant. Le choix du rapport signal-à-bruit se fait grâce aux interrupteurs selon la table de correspondance donnée en annexe A. En utilisant un interrupteur on peut arrêter et relancer la détection d'erreurs à tout moment. Le résultat du calcul de taux d'erreurs binaires est indiqué sur les afficheurs 7 segments. De plus, deux signaux représentant respectivement le nombre d'erreurs et le nombre total de bits sont générés pour permettre le debug par simulation.

Cible matérielle⚓

Le matériel utilisé est composé d’un PC et d’une carte électronique intégrant,

- le circuit intégré programmable FPGA (Field Programmable Gate Array) de type Artix-7 de Xilinx, sur une carte Nexys4 de Digilent

- les afficheurs 7 segments,

- les interrupteurs,

- les boutons poussoirs,

- un oscillateur à 100 MHz, pour fournir un signal d'horloge.

La figure suivante présente les différents éléments présents sur la carte. L’outil de conception de circuit, installé sur le PC (ou disponible à distance), est Vivado de Xilinx.

En supplément, on utilise une carte de conversion numérique-analogique (CNA) pour visualiser les signaux I et Q en sortie du canal à l'oscilloscope.

Circuit complet de MAQ16⚓

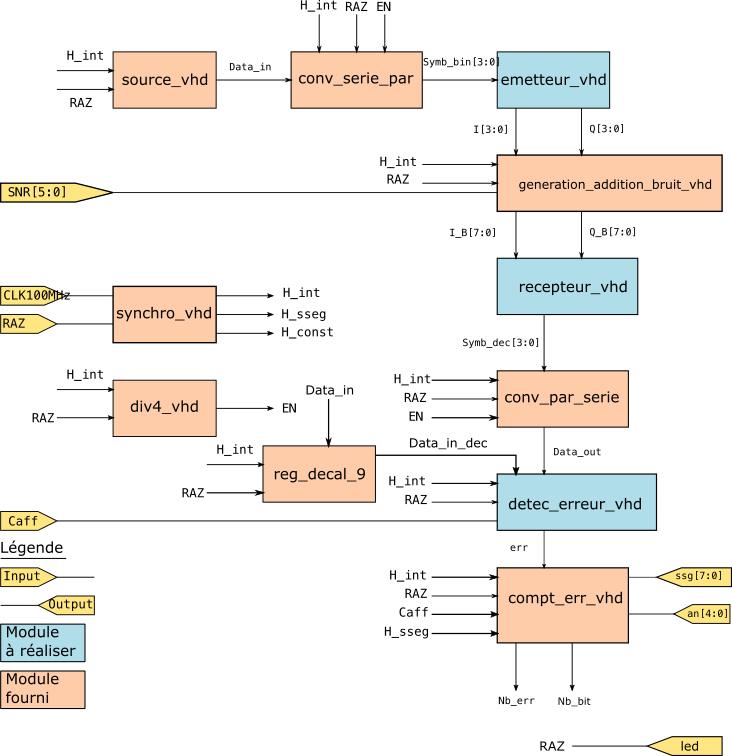

L'architecture du circuit complet est décrite figure suivante. Les blocs saumon sont fournis complet, ils n'ont pas à être modifiés. Les blocs bleu doivent être modifiés. Les ports d'entrée et sortie du circuit FPGA sont représentés en jaune. Toutes les flèches représentent des signaux internes au circuit FPGA.

Principe de fonctionnement⚓

Avant de lancer l'émulation de la transmission de données, il faut initialiser le circuit en positionnant RAZ à 1, puis en le remettant en 0. Le passage à 0 de RAZ lance la génération des données binaires par le module source. Après conversion série parallèle, les quatre bits du symbole de modulation MAQ16 entrent dans le module emetteur, qui les convertit en signaux I et Q. Les 6 interrupteurs SNR permettent de programmer l'écart-type du bruit ajouté par le module generation_addition_bruit. Les signaux I et Q sont alors bruités à l'aide de ce module. Les signaux bruités I_B et Q_B sont ensuite détectés par le module recepteur pour obtenir le symbole de modulation décidé. Après conversion parallèle série, la séquence de données binaires décidées est comparée à la séquence de données émises à l'aide du module detect_err. Le module compt_err compte les erreurs et fournit deux signaux de sortie qui correspondent au nombre d'erreurs et au nombre de bits total émis. Il fournit également deux signaux permettant d'afficher le résultat sur les afficheurs 7 segments. L'interrupteur Caff permet d'arrêter et de relancer la détection des erreurs.

Description des modules existants⚓

Module synchro_vhd⚓

Ce bloc fournit à partir de l'oscillateur CLK100MHz les différents signaux d'horloges du FPGA. Ces signaux sont nécessaires au fonctionnement du circuit global.

Entrées :

CLK100MHz: signal en provenance de l’oscillateur de la carte Digilent.RAZ: signal de remise à zéro actionné par un bouton sur la carte Digilent.

Sortie :

H_int: obtenue par division de 256 deCLK100MHz. C'est l'horloge débit des données.H_sseg: obtenue par division de fréquence deCLK100MHz. C'est l'horloge permettant l'affichage du résultat.H_const: obtenue par division de fréquence deCLK100MHz. Horloge non utilisée.

Module div4_vhd⚓

Le bloc div4_vhd fournit un signal de contrôle EN utilisé par le bloc emetteur et le bloc recepteur. Ce module est un compteur modulo 4 dont un des 4 états est décodé : EN est à 1 pendant une période d'horloge et à 0 pendant les 3 autres. Ce signal est nécessaire au séquencement de la conversion série-parallèle et parallèle-série. Il doit être utilisé en ENABLE et non en signal d'horloge.

Entrée : \begin{itemize}

H_int: signal en provenance du bloc synchroRAZ: signal de remise à zéro actionné par un bouton sur la carte FPGA.

Sortie :

EN: signal de type Enable égal à1pendant une période deH_intsur 4.

Module source_vhd⚓

La source fournit sur data_in une séquence pseudo-aléatoire de période \(2^{31}-1\), au rythme de H_int.

Entrées : \begin{itemize}

H_int: signal en provenance du bloc synchroRAZ: signal d'initialisation au démarrage du circuit

Sortie

Data_in: signal de données binaires pseudo-aléatoires en série,

Module compteur_err_vhd⚓

Le bloc compt_err_vhd réalise le comptage des erreurs et gère l’affichage du taux d’erreurs binaires. Le comptage des erreurs est effectué sur des séquences de 1 Mbits. Le bloc gère ensuite l’affichage de ce nombre sur les 4 afficheurs 7 segments de la carte. La lecture se fait comme suit : le nombre d'erreurs est égal au nombre affiché par les 3 afficheurs de gauche multiplié par une puissance de 10 négative fournie par le 4ème afficheur. Exemple : sur la figure ci-dessous on lit le taux d'erreurs binaires \(606.10^{-4}\), c'est à dire \(6,06.10^{-2}\). Le signal nb_err comptabilise le nombre d'erreurs. Le signal nb_bits compte le nombre de bits depuis le début de la détection d'erreurs. Le démarrage de la détection d'erreurs est piloté par le signal Caff.

Entrée

H_int: signal en provenance du bloc synchroRAZ: signal d'initialisation au démarrage du circuitCaff: signal d'arrêt et de relance de la détection d'erreursH_sseg: obtenue par division de fréquence de CLK100MHz. C'est l'horloge permettant l'affichage du résultat.err: égal à1lorsqu’une erreur est détectée à la réception

Sorties

s_aff[7:0]: permet l'affichage du taux d’erreurs binaires sur les afficheurs 7 segmentsan[4:0]: permet le choix de l'afficheurNb_err: donne le nombre d'erreurs depuis le début du comptageNb_bit: donne le nombre de bits passés dans le canal depuis le début du comptage

Module generation_addition_bruit_bhd⚓

Ce bloc génère des échantillons de bruit blanc de distribution gaussienne et les ajoute aux symboles représentés par les voies I et Q. L'écart-type des échantillons de bruit est programmable à l’aide des interrupteurs présents sur la carte d’interface. La table de correspondance entre les interrupteurs SNR[5:0], l'écart-type et le rapport signal-à-bruit est donnée en annexe A (cf. section \ref{sec:TP4_annexeA}). Ce module suppose que les symboles non bruités fournis sur les voies I et Q sont codés en complément à 2. Les symboles bruités sont fournis sur 8 bits : 4 bits pour la partie entière et 4 bits pour la partie fractionnaire. La partie fractionnaire ne sert que pour la visualisation de la constellation.

Entrées :

I[3:0]: signal représentant la voie en phase de la MAQ16 codée en complément à 2 sur 4 bitsQ[3:0]: signal représentant la voie en quadrature de la MAQ16 codée en complément à 2 sur 4 bits

Sorties :

I_B[7:0]: signal représentant la voie en phase bruitée en complément à 2 sur 8 bitsQ_B[7:0]: signal représentant la voie en quadrature bruitée en complément à 2 sur 8 bits

Module conv_serie_par⚓

Ce module réalise la conversion série parallèle du flux de données data_in vers une séquence de mots de 4 bits, constituant le 4-uplet du symbole de modulation MAQ16. Il utilise le signal EN, actif tous les 4 cycles d'horloge, généré par diviseur_freq.

Entrées :

data_in: signal de données binaires en série,H_int: signal en provenance du module synchro,EN: signal de type Enable égal à1pendant une période deH_intsur 4.

Sortie :

symb_bin[3:0]: séquence de mots de 4 bits, constituant le 4-uplet du symbole de modulation MAQ16.

Module conv_par_serie⚓

Ce module réalise la conversion parallèle série des données décidées issues du module recepteur. Il utilise le signal EN, actif tous les 4 cycles d'horloge, généré par div4_vhd.

Entrées :

symb_dec[3:0]: séquence de mots de 4 bits, constituant le 4-uplet du symbole de modulation MAQ16 après décision.H_int: signal en provenance du module \verb+synchro+,EN: signal de type Enable égal à 1 pendant une période de \verb+H_int+ sur 4.

Sortie :

Data_out: signal de données binaires décidées en série

Cahier des charges des modules à concevoir⚓

Les fonctionnalités des trois modules à concevoir sont décrites ci-dessous.

Module emetteur_vhd⚓

Ce module combinatoire fournit les valeurs numériques de type réel signé en codage en complément à 2 sur 4 bits (pour chaque voie) des symboles modulés en MAQ16. La voie I donne la voie en phase et la voie Q donne la voie en quadrature. Le mapping qui répond aux deux contraintes suivantes est donné en annexe :

- Minimisation de la probabilité d’erreur

- Simplification de la détection des symboles au niveau du récepteur

Entrée :

symb_bin[3:0]: séquence de mots de 4 bits, constituant le 4-uplet du symbole de modulation MAQ16.

Sorties :

I[3:0]: séquence représentant la voie en phase de la MAQ16 codée en complément à 2 sur 4 bits (uniquement partie entière, car nombre entier signé)Q[3:0]: séquence représentant la voie en quadrature de la MAQ16 codée en complément à 2 sur 4 bits (uniquement partie entière, car nombre entier signé)

Module recepteur_vhd⚓

Ce module réalise la détection des symboles bruités reçus. Pour cela, il reçoit les valeurs numériques codées en complément à 2 sur 8 bits de la voie en phase et la voie en quadrature représentant les symboles bruités. Seule la partie entière de ces valeurs numériques en complément à 2 sur 4 bits des symboles bruités sera utilisée pour réaliser la détection. Ce module fournit sur symb_dec[3:0] le 4-uplet du symbole de modulation décidé. Les règles de décision pour les voies I et Q sont données dans le TD de préparation en annexe

Entrées :

I_B[7:0]: séquence représentant la voie en phase de la MAQ16 codée et bruitée en complément à 2 sur 8 bits, dont 4 bits de partie entièreQ_B[7:0]: séquence représentant la voie en quadrature de la MAQ16 codée et bruitée en complément à 2 sur 8 bits, dont 4 bits de partie entière

Sortie :

symb_dec[3:0]: séquence de mots de 4 bits, constituant le 4-uplet du symbole de modulation MAQ16 qui a été détecté.

Module detect_err_vhd⚓

Ce module réalise la détection d’erreur. Pour cela, les signaux Data_in_dec et Data_out sont comparés. Si les signaux sont différents, la sortie err est égale à 1 et égale à 0 dans le cas contraire. Pour que la comparaison se fasse correctement, Data_in a été retardé d'un nombre de périodes égal à la latence de la chaîne de transmission. Ce retard est appliqué dans le module reg_decal_9. Remarque : le générateur de bruit n'introduit aucune latence.

Enfin, le signal Caff permet de relancer la détection d’erreurs à tout moment en interrompant la détection d’erreurs. Ce signal est directement relié à un bouton poussoir sur la carte. Le signal Caff peut être considéré comme un signal de validation du signal err.

Entrées :

H_int: signal en provenance du bloc synchroRAZ: signal d'initialisation au démarrage du circuitCaff: signal d'arrêt et de relance de la détection d'erreursData_out: signal de données binaires décidées en sérieData_in_dec: signal de données binaires pseudo-aléatoires en série, retardé d'un nombre de périodes égal à la latence de la chaîne de transmission.

Sortie :

err: signal d'erreur égal à 0 si le bit détecté n'est pas erroné et 1 s'il y a une erreur.

Travaux pratiques en séance⚓

Phase 1 - Description et simulation des modules combinatoires⚓

Création du projet⚓

Téléchargement de l'archive source⚓

Une archive de fichiers sources vous est proposée sur https://moodle.imt-atlantique.fr/course/view.php?id=578#section-1. Cette archive, appelée SIT212_TP4_Source_files_vivado.tar.gz, vous permet de récupérer les fichiers sources VHDL de description et de simulation.

Une fois téléchargée, elle doit être décompressée dans un répertoire de travail que vous aurez judicieusement créé dans votre arborescence de fichiers, comme ~/SIT212/TP4/Fichiers_sources par exemple.

Warning

Ne mettez jamais d'espaces, d'accents ou des caractères spéciaux dans les noms de répertoires ou de fichiers

Ouverture de Vivado⚓

Sous Linux, ouvrez un Terminal (Ctrl+Alt+T) et lancez la commande suivante

1 | |

Création d'un nouveau projet⚓

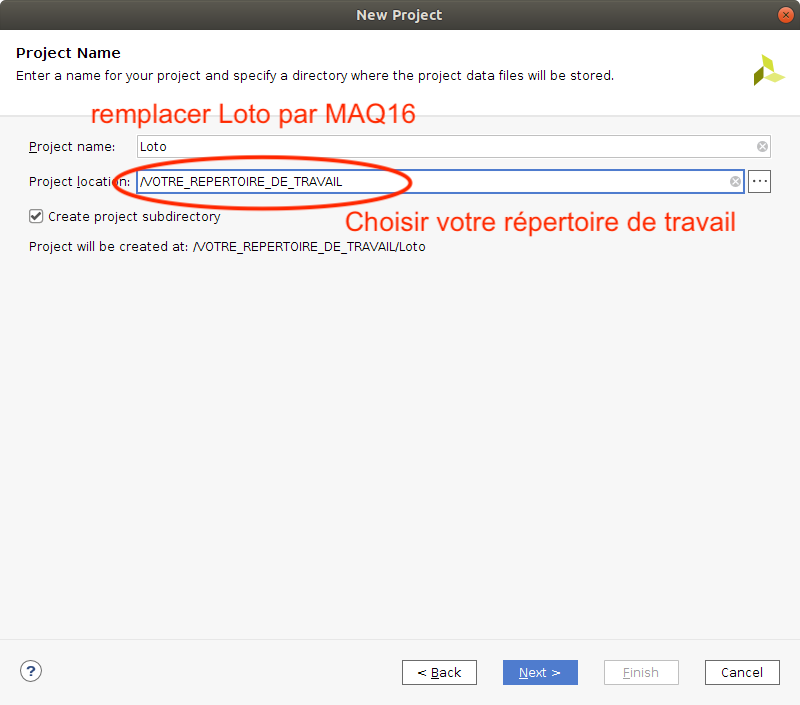

Cliquez sur Create Project pour lancer l'assistant (wizard) de création de projet, puis cliquez sur Next sur la fenêtre qui apparaît alors.

Dans la fenêtre suivante (figure suivante), renseignez le nom de votre projet (MAQ16) et votre répertoire de travail ~/SIT212/TP4. Create project directory doit être coché.

A la fenêtre suivante (figure suivante), sélectionnez RTL Project pour créer un projet qui acceptera des sources VHDL.

Ajout des fichiers sources et des contraintes⚓

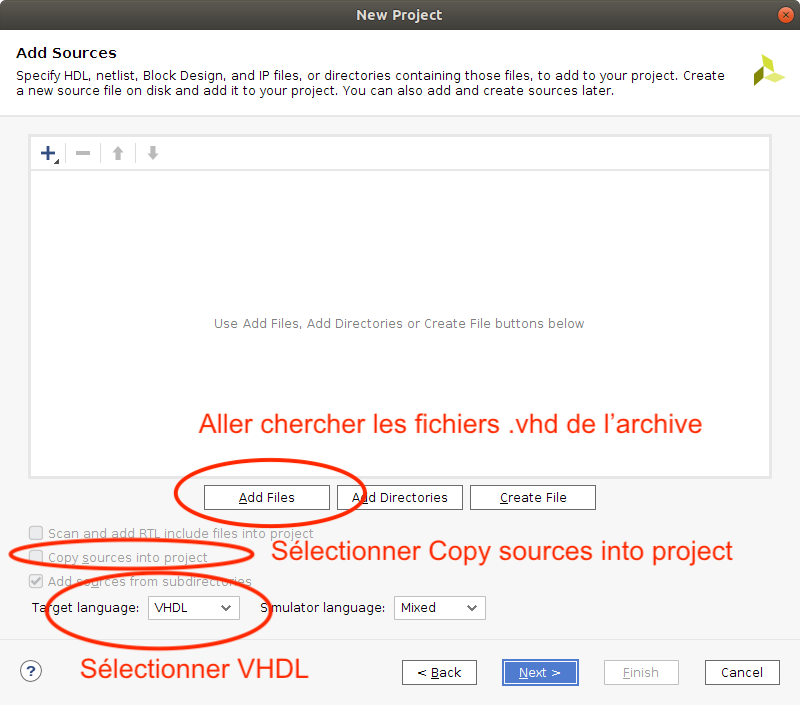

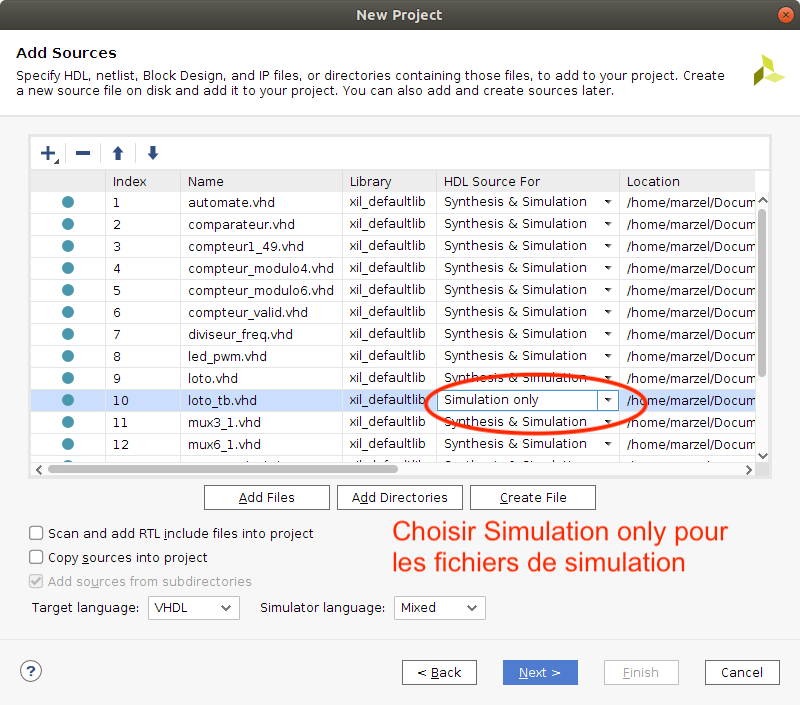

Validez encore avec Next pour passer à la fenêtre suivante qui vous demande vos fichiers sources (figure suivante).

Sélectionnez alors tous les fichiers VHDL (en extension .vhd) de votre archive décompressée disponible dans les dossiers sources et sim. Puis modifiez le mode des fichiers de test, qui commencent par TB ou tb, en mode Simulation uniquement comme en figure suivante.

- Sélectionnez Copy sources into project.

- Sélectionnez Target langage VHDL.

- Cliquez sur Next pour valider.

Ne renseignez rien dans la fenêtre suivante (aucun module autre que décrit en VHDL ne sera utilisé) et continuez.

Sélection du FPGA utilisé⚓

Apparaît alors la fenêtre Add Constraints. Sélectionnez le fichier MAQ16_Top.xdc dans le répertoire constrs.

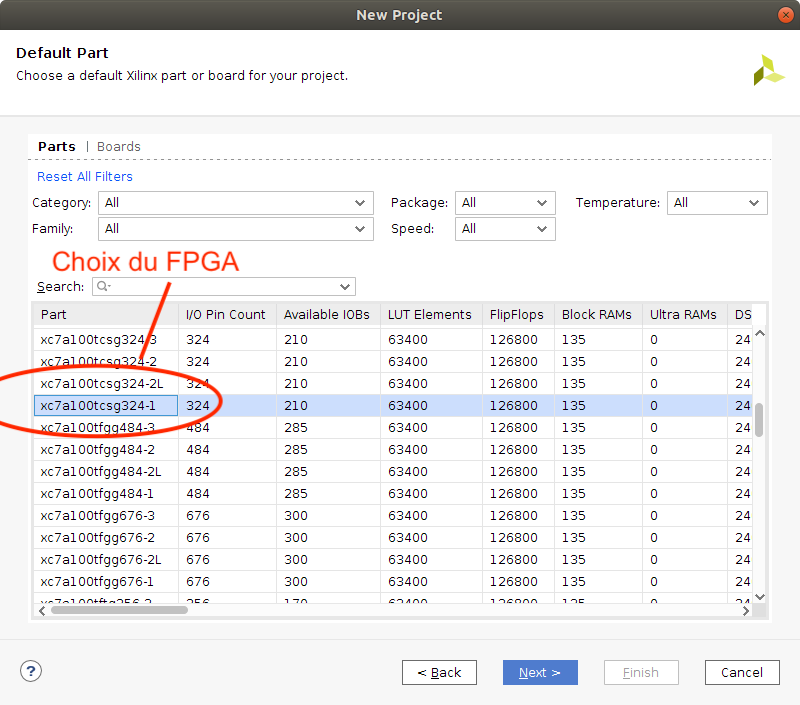

Après validation apparaît la fenêtre de sélection de la cible matérielle FPGA que vous renseignez tel qu'indiqué sur la figure suivante. Cela vous permet de choisir le FPGA de la carte (xc7a100tcsg324-1 de son petit nom).

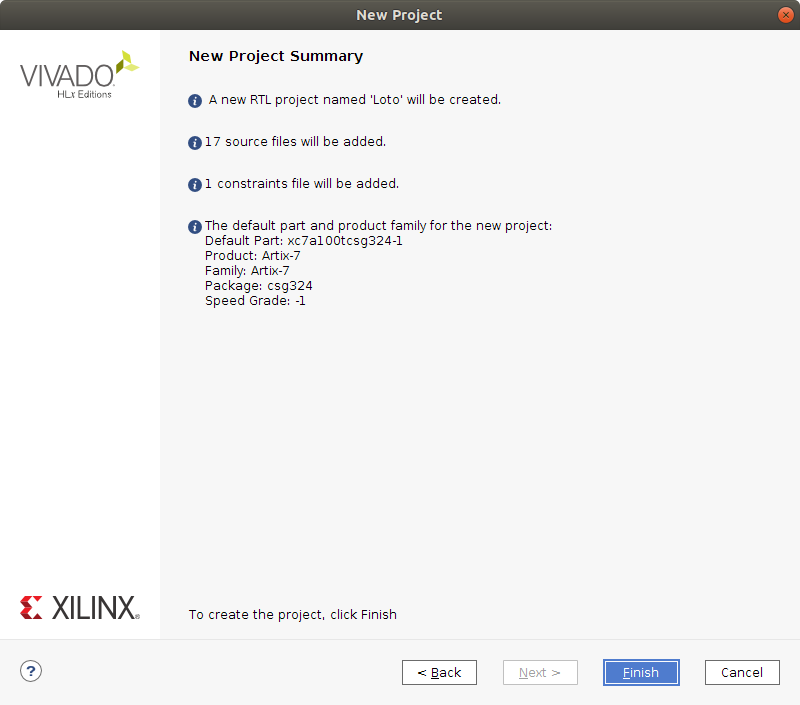

La fenêtre suivante résume votre projet et doit être identique à celle présentée en figure suivante.

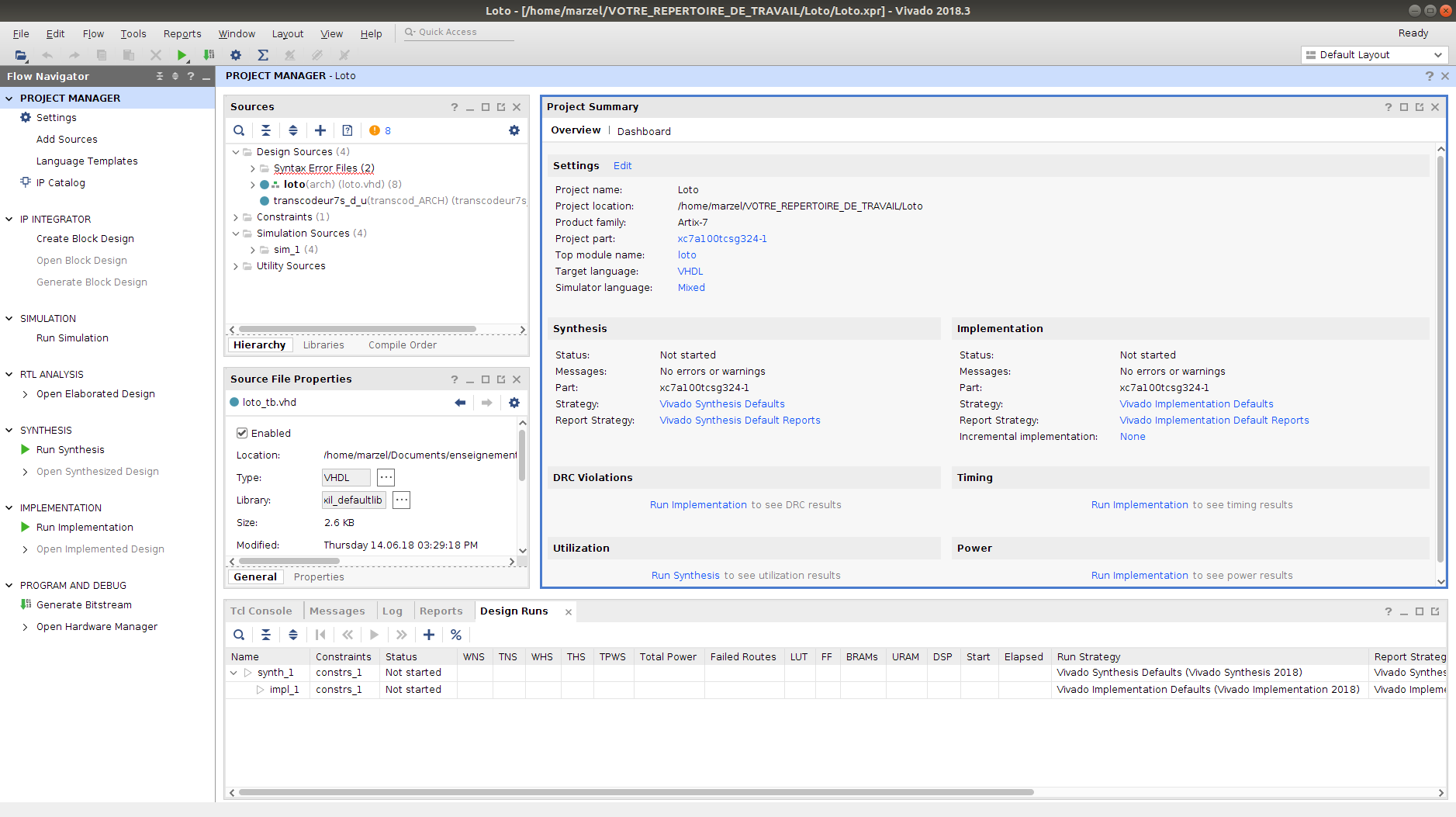

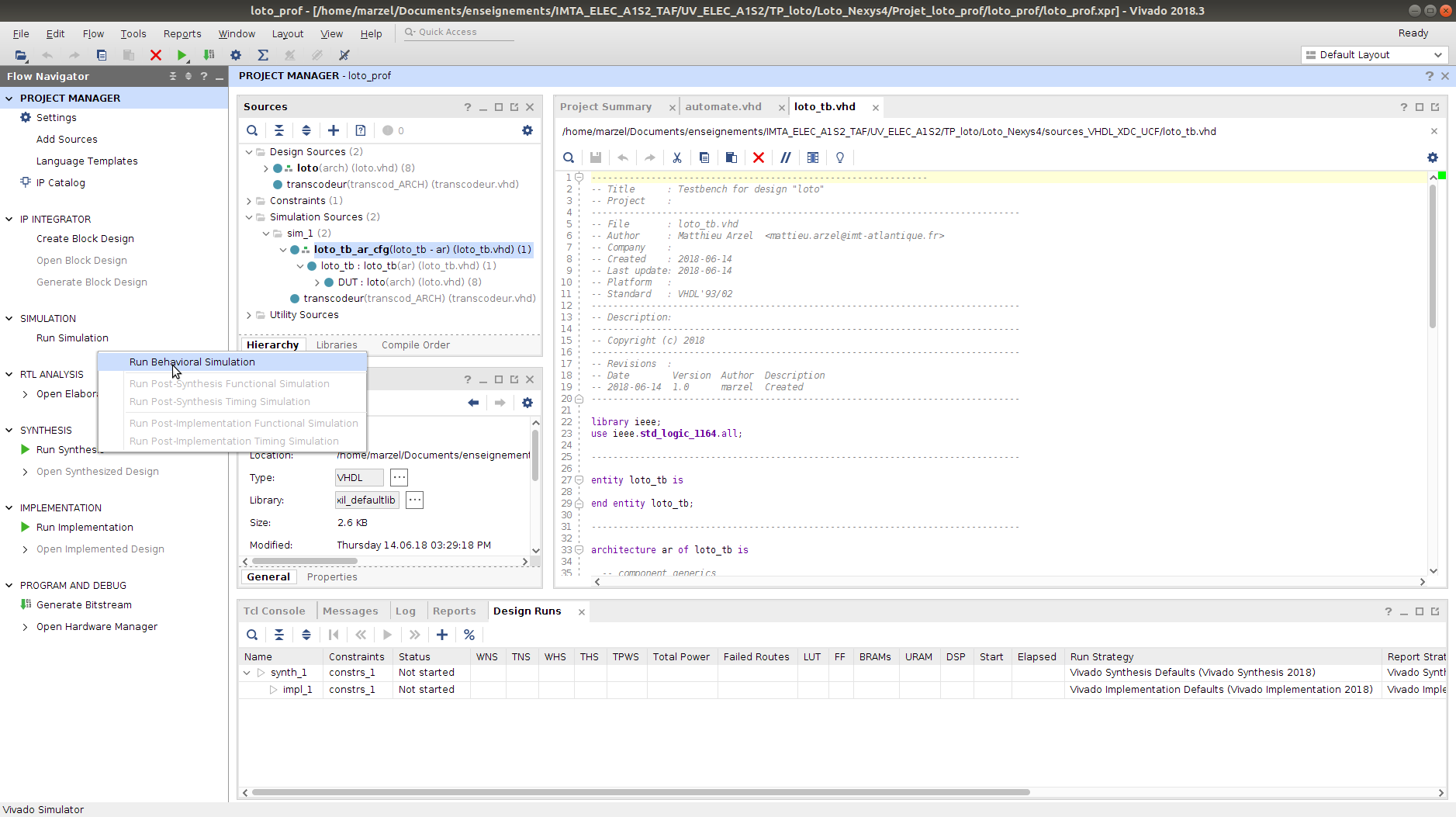

Le projet est ensuite créé et l'interface projet de Vivado se lance comme en figure suivante.

Description partielle du module combinatoire emetteur_vhd en VHDL⚓

- Dans la fenêtre PROJECT MANAGER / Sources développez l'onglet

Design Sources. Puis MAQ16_Top. - Ouvrez le fichier

emetteur_vhd.vhd, dont certaines parties ont été remplacées par_BLANK_. - À partir de votre travail préparatoire sous la forme d'une table de vérité, et de la description VHDL de la structure

casedécrite dans l'Aide-mémoire VHDL, - remplacez les sections

_BLANK_par du code approprié.

Question 1

- À quoi servent les signaux intermédiaires

I_intetQ_int? En quoi est-ce lié au choix du mapping MAQ16 ? - Consultez la section Examples-of-synthesizable-vhdl de l'Aide-mémoire VHDL pour comprendre la notion de

processet de liste de sensibilité (sensitivity list) des processus asynchrones (c.a.d. combinatoires). Dans le cadre de ce moduleemetteur_vhd, quels sont les signaux à renseigner dans la liste de sensibilité de chacun des 2 processus ? Pourquoi ? - Expliquez la notion de processus concurrents.

Simulation VHDL du module emetteur_vhd⚓

Pour valider ensuite votre module emetteur_vhd, vous le simulez avec l'outil XSIM de Vivado.

Pour cela un fichier de test vous est proposé: TB_emetteur.vhd, aussi disponible par la fenêtre Sources, onglet Simulation Sources / sim_1. Sélectionnez ce module.

Puis, cliquez sur le bouton droit de la souris pour faire apparaître le menu contextuel et cliquez sur Set as Top. Ainsi, ce module pourra être simulé en cliquant dans le panneau de gauche Flow Navigator / Project Manager sous l'onglet Simulation

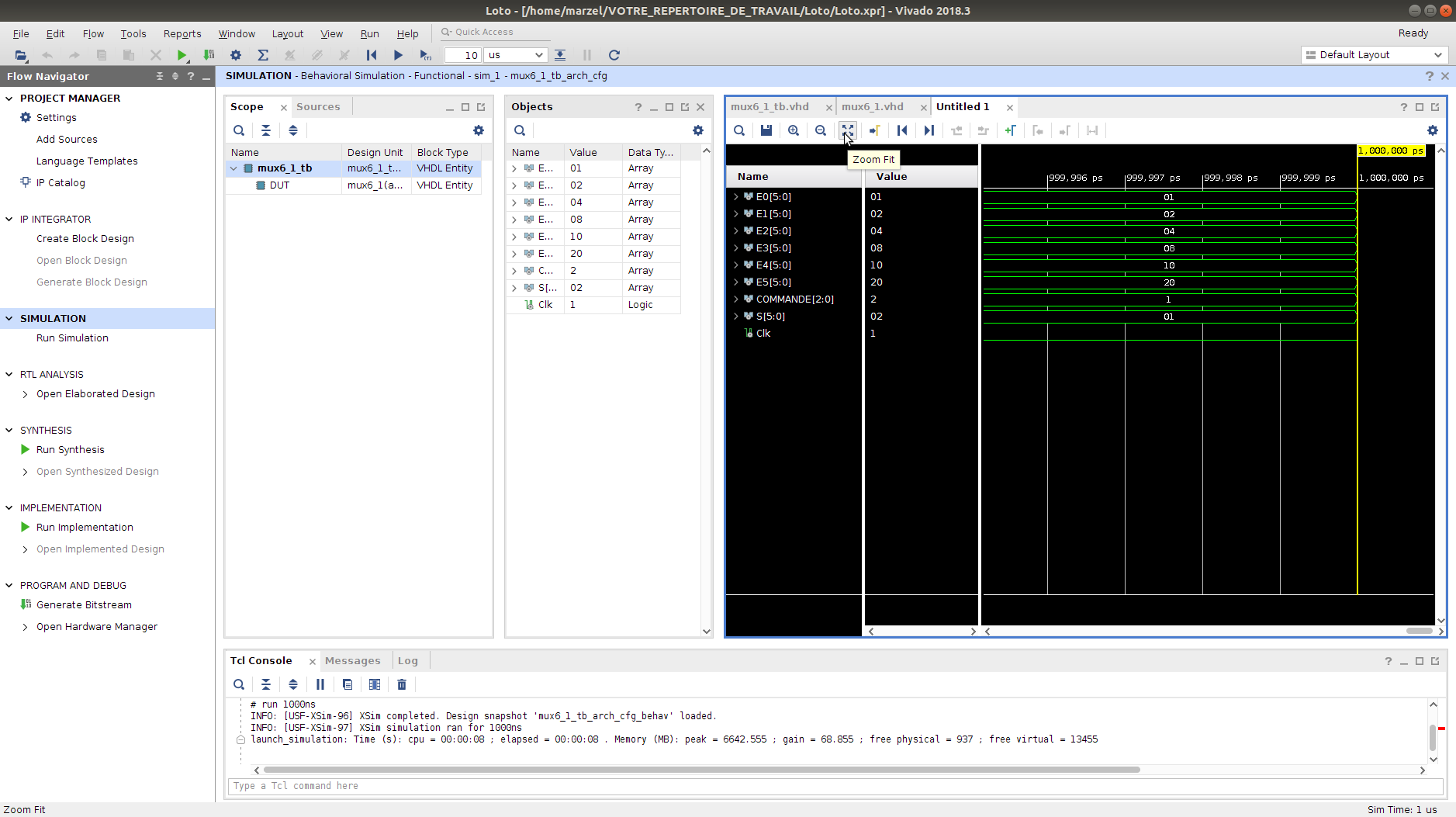

La fenêtre illustrée en figure suivante apparaît alors.

Choix du Zoom

Cliquez sur Zoom Fit puis ajustez le zoom jusqu'à pouvoir analyser le chronogramme de la simulation et ainsi vérifier que votre description VHDL fournit le comportement attendu.

Format de représentation des nombres dans la simulation

Dans le chronogramme résultat de la simulation, chaque signal binaire affiché peut être représenté sous différents formats : binaire naturel, réel signé, réel non signé, hexadécimal, etc. Cette représentation (ou radix d'affichage) est au choix du concepteur et peut être choisi afin de faciliter la lecture des résultats de simulation. Par exemple, pour modifier le radix d'affichage d'un signal en décimal non signé cliquez sur le nom d'un signal, avec le bouton DROIT de la souris, puis sur radix > unsigned decimal.

Tip

Choisissez astucieusement les représentations de vos signaux d'entrée et sortie pour vous faciliter la tâche d'analyse de la simulation.

Question 2

Toutes les réponses aux questions doivent être illustrées par des copies écrans des simulations.

- Justifiez vos choix de format de représentation des nombres pour les signaux d'entrée et de sortie.

- Observez le résultat de simulation et analysez-le. Observez également le fichier de testbench. Pourquoi cette simulation ne permet-elle pas de valider le module de manière complète et exhaustive ?

- En lien avec la question précédente, modifiez le ficher de testbench, et relancez la simulation.

- Analysez le résultat de cette 2ieme simulation et justifiez la validation du module.

Description partielle du module combinatoire recepteur_vhd en VHDL⚓

- Quittez la simulation en fermant la sous-fenêtre de simulation.

- Dans la fenêtre PROJECT MANAGER / Sources développez l'onglet Design Sources.

- Ouvrez le fichier

recepteur_vhd.vhd, dont certaines parties ont été remplacées par_BLANK_.

À partir de votre travail préparatoire sous la forme de fonctions logiques, et de la description VHDL des fonctions logiques combinatoires décrites dans l'Aide mémoire VHDL, remplacez les sections _BLANK_ par du code approprié.

Question 3

- Quels sont les bits de

IetQqui correspondent à la partie entière des nombres qu'ils représentent ? - Expliquez pourquoi seule la partie entière est utilisée dans l'obtention du symbole décidé

b_int(ouSymb_dec) et le rôle de la troncature par défaut dans la règle de décision du bitSymb_dec[2]} etSymb_dec[0]. - Expliquez pourquoi cela réduit la complexité du circuit qui sera généré.

Simulation VHDL du module recepteur_vhd⚓

Pour valider de nouveau votre description VHDL, vous devez simuler le module avec le fichier de test proposé: TB_recepteur.vhd. Pour cela, cliquez sur ce fichier puis clic bouton droit de la souris et choisissez Set As Top. Puis effectuez la simulation comme précédemment.

Dans le chronogramme, les signaux I et Q sont représentés sur 8 bits. Pour faciliter la lecture, nous souhaitons récupérer uniquement les 4 bits de poids forts. Pour cela, dans la fenêtre Objects, développez I_B[7:0] et Q_B[7:0]. Glissez-déposez les signaux correspondants aux bits de poids forts dans la fenêtre qui liste les signaux du chronogramme (sous Name). Toujours en gardant les 4 signaux correspondant aux bits de poids fort sélectionnés, cliquez DROIT et choisissez New virtual bus. Donnez lui un nom explicite. }

Pour faciliter la lecture, vous pouvez changer le radix d'affichage. En particulier, pour les signaux d'entrée, vous pouvez utiliser Real settings puis choisir fixed point, signed, binary point 4. Pour les bits de poids fort (la partie entière après troncature), choisissez signed decimal.

Question 4

Toutes les réponses aux questions doivent être illustrées par des copies écrans.

- Observez et analysez le résultat de la simulation. À quoi comparez-vous le résultat de votre simulation ? En quoi cette simulation valide-t-elle fonctionnellement le module ?

- À partir de la simulation, donnez des exemples de troncatures pour des signaux reçus

I_BetQ_Bpositifs et négatifs. Expliquez les décisions prises au niveau binaireSymb_dec[3:0]au regard des règles de décision de la MAQ16.

Description partielle du module combinatoire detect_err en VHDL⚓

- Quittez la simulation en fermant la sous-fenêtre de simulation.

- Dans la fenêtre PROJECT MANAGER / Sources développez l'onglet Design Sources.

- Ouvrez le fichier

detect_err_vhd.vhd, dont certaines parties ont été remplacées par_BLANK_.

À partir de votre travail préparatoire sous la forme de fonctions logiques, et de la description VHDL des fonctions logiques combinatoires décrites dans l'Aide mémoire VHDL, remplacez les sections _BLANK_ par du code approprié.

Simulation VHDL du module detect_err⚓

Pour valider de nouveau votre description VHDL, vous devez simuler le module avec le fichier de test proposé: TB_detect_err.vhd. N'oubliez pas Set As Top.

Phase 2 - Simulation et test du circuit complet⚓

Pour valider par simulation l'intégration des 3 modules, vous devez simuler l'intégralité du circuit de MAQ16.

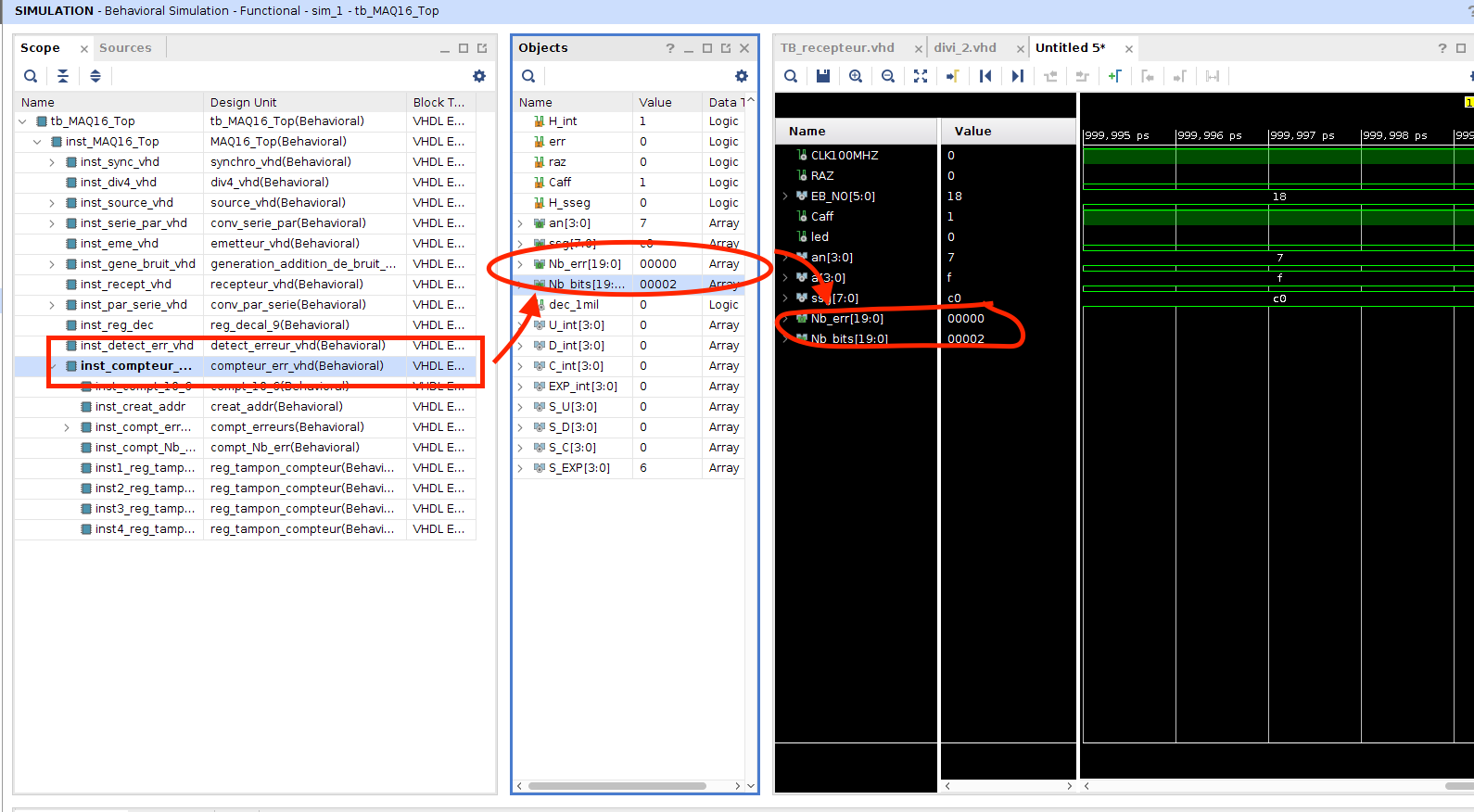

Passez donc le module tb_MAQ16_Top.vhd en TOP et simulez le circuit comme illustré en figure suivante.

Cependant, les signaux Nb_err et Nb_bits, qui ne font pas partie des ports d'entrée/sortie du circuit, n'apparaissent pas. Pour les ajouter à la simulation, dans la fenêtre SIMULATION / Scope développez inst_MAQ16_Top puis cliquez sur inst_compteur_erreur_vhd. Dans la fenêtre SIMULATION / Objects glissez-déposez les signaux Nb_err et Nb_bits dans la fenêtre de simulation pour les faire apparaître dans la liste de signaux à simuler :

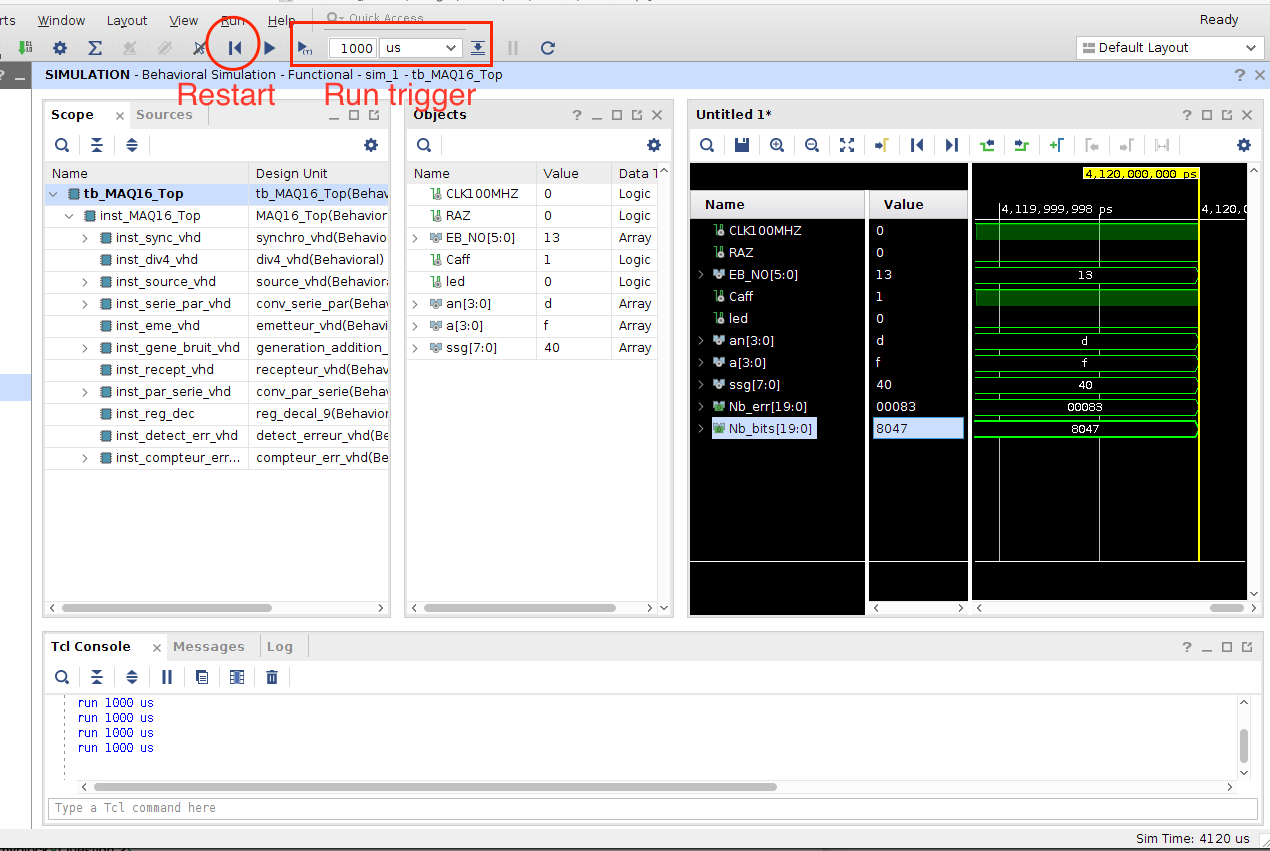

Puis cliquez sur Restart. Enfin, cliquez sur Run trigger :

Question 5

Toutes les réponses aux questions doivent être illustrées par des copies écrans des simulations.

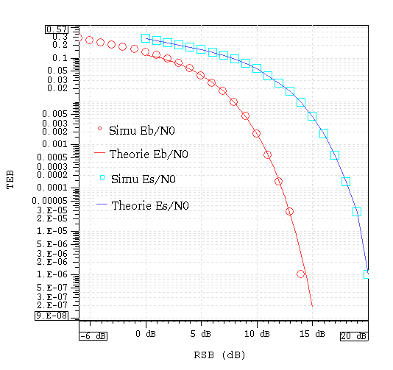

La correspondance entre le signal SNR[5:0] et \(SNR = E_s/N_0\) en dB est donnée dans le tableau des SNR. Les courbes théorique et simulée sous MATLAB de la probabilité d'erreur de la MAQ16 sont données figure TEB MAQ 16.

- Expliquez pourquoi aucune erreur n'est détectée (

Nb_errest égal à 0) lors du 1er lancement de la simulation. - Que se passe-t-il lorsqu'on relance la simulation en cliquant plusieurs fois sur Run trigger ?

- Quel est le taux d'erreurs obtenu ? Pour quelle valeur du signal

SNR[5:0]et donc quelle valeur de SNR en dB (cf. tableau des SNR) ? Est-ce que cela correspond à la courbe théorique donnée à la figure TEB MAQ 16 ? (\(SNR = E_s/N_0\)) - Vérifiez un autre point de la courbe en modifiant le signal

SNR[5:0]dans le fichier de testbench. Vous placez les points directement sur la figure (faîtes une copie écran). - Dans le fichier de simulation

tb_MAQ16_Top.vhd, modifiez le signalSNR[5:0]pour qu'il représente une valeur de 24,02 dB, puis relancez la simulation pour vérifier le nouveau taux d'erreurs. Qu'observez-vous ? Pourquoi ?

⚓

SNR[5:0] |

\(\sigma_b\) | \(SNR\) (dB) | SNR[5:0] |

\(\sigma_b\) | \(SNR\) (dB) |

|---|---|---|---|---|---|

| 000001" | 110111 | 8,3 | 100001" | 10110 | 16,26 |

| 000010" | 110101 | 8,62 | 100010" | 10101 | 16,67 |

| 000011" | 110100 | 8,79 | 100011" | 10100 | 17,09 |

| 000100" | 110010 | 9,13 | 100100" | 10100 | 17,09 |

| 000101" | 110001 | 9,31 | 100101" | 10011 | 17,54 |

| 000110" | 101111 | 9,67 | 100110" | 10011 | 17,54 |

| 000111" | 101110 | 9,86 | 100111" | 10010 | 18 |

| 001000" | 101101 | 10,05 | 101000" | 10010 | 18 |

| 001001" | 101011 | 10,44 | 101001" | 10001 | 18,5 |

| 001010" | 101010 | 10,65 | 101010" | 10001 | 18,5 |

| 001011" | 101001 | 10,86 | 101011" | 10000 | 19,03 |

| 001100" | 101000 | 11,07 | 101100" | 10000 | 19,03 |

| 001101" | 100111 | 11,29 | 101101" | 1111 | 19,59 |

| 001110" | 100110 | 11,52 | 101110" | 1111 | 19,59 |

| 001111" | 100100 | 11,99 | 101111" | 1110 | 20,19 |

| 010000" | 100011 | 12,23 | 110000" | 1110 | 20,19 |

| 010001" | 100010 | 12,48 | 110001" | 1101 | 20,83 |

| 010010" | 100001 | 12,74 | 110010" | 1101 | 20,83 |

| 010011" | 100000 | 13,01 | 110011" | 1101 | 20,83 |

| 010100" | 100000 | 13,01 | 110100" | 1100 | 21,53 |

| 010101" | 11111 | 13,29 | 110101" | 1100 | 21,53 |

| 010110" | 11110 | 13,57 | 110110" | 1100 | 21,53 |

| 010111" | 11101 | 13,86 | 110111" | 1011 | 22,28 |

| 011000" | 11100 | 14,17 | 111000" | 1011 | 22,28 |

| 011001" | 11011 | 14,48 | 111001" | 1011 | 22,28 |

| 011010" | 11010 | 14,81 | 111010" | 1010 | 23,11 |

| 011011" | 11010 | 14,81 | 111011" | 1010 | 23,11 |

| 011100" | 11001 | 15,15 | 111100" | 1010 | 23,11 |

| 011101" | 11000 | 15,51 | 111101" | 1001 | 24,02 |

| 011110" | 11000 | 15,51 | 111110" | 1001 | 24,02 |

| 011111" | 10111 | 15,88 | 111111" | 1001 | 24,02 |

| 100000" | 10110 | 16,26 | AUTRES | 111000 | 8,15 |

ref section Module generation_addition_bruit_bhd : annexe : est donnée en annexe A (cf. section \ref{sec:TP4_annexeA})

ref section cdc Module emetteur_vhd l'annexe D (cf. section \ref{sec:TP4_annexeA})

ref section cdc recepteur_vhd (cf .Annexe \ref{sec:TP4_annexeC}).

ref !!! question "Question 5" \ref{tab:snr}

ref !!! question "Question 5" \ref{fig:maq16_teb}.

ref !!! question "Question 5" (cf. tableau \ref{tab:snr})